Project Overview

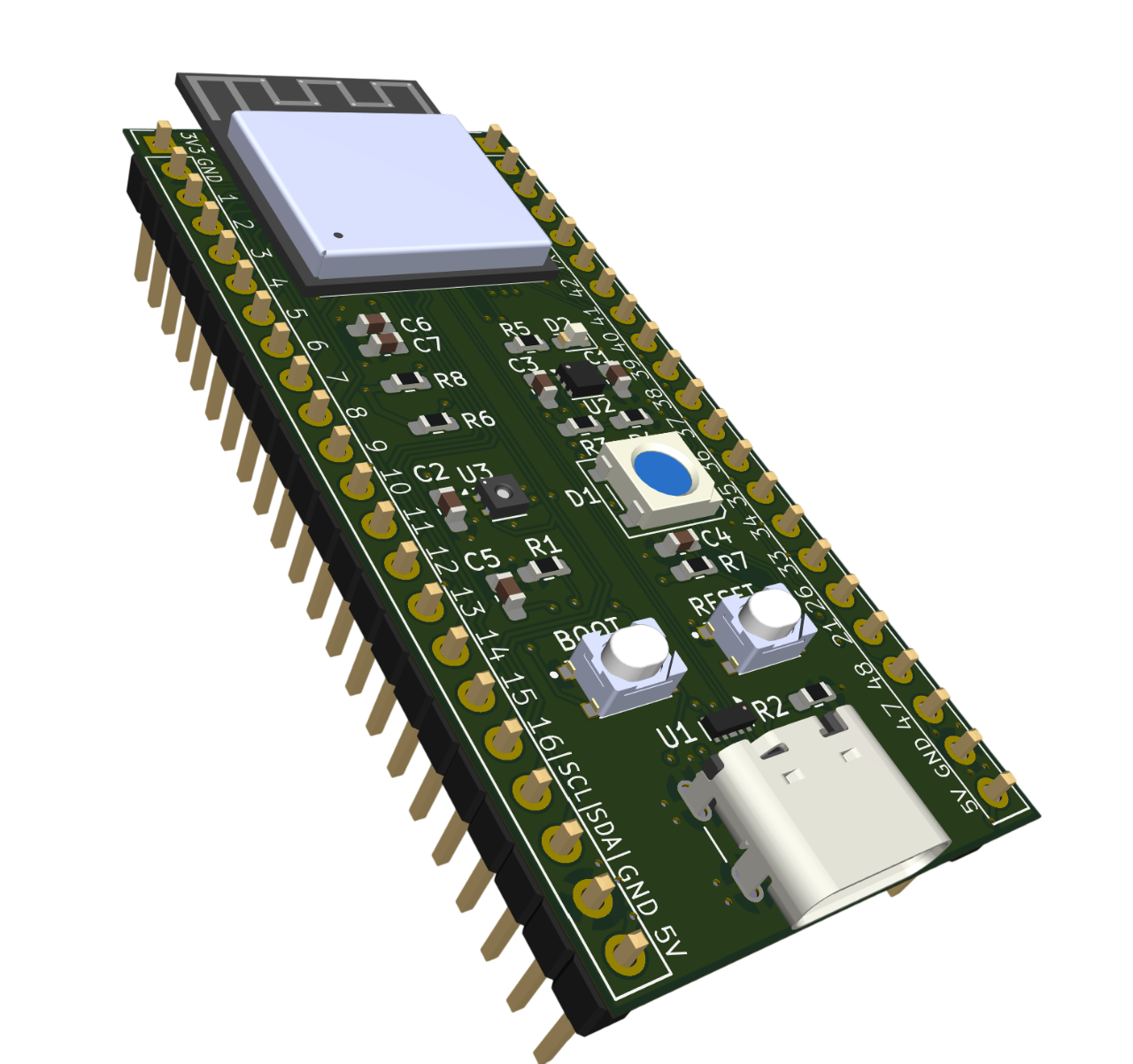

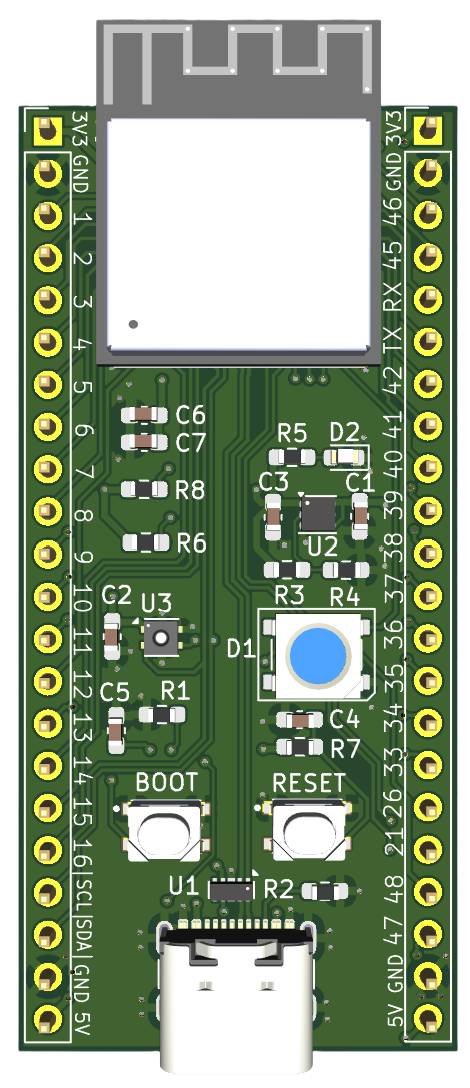

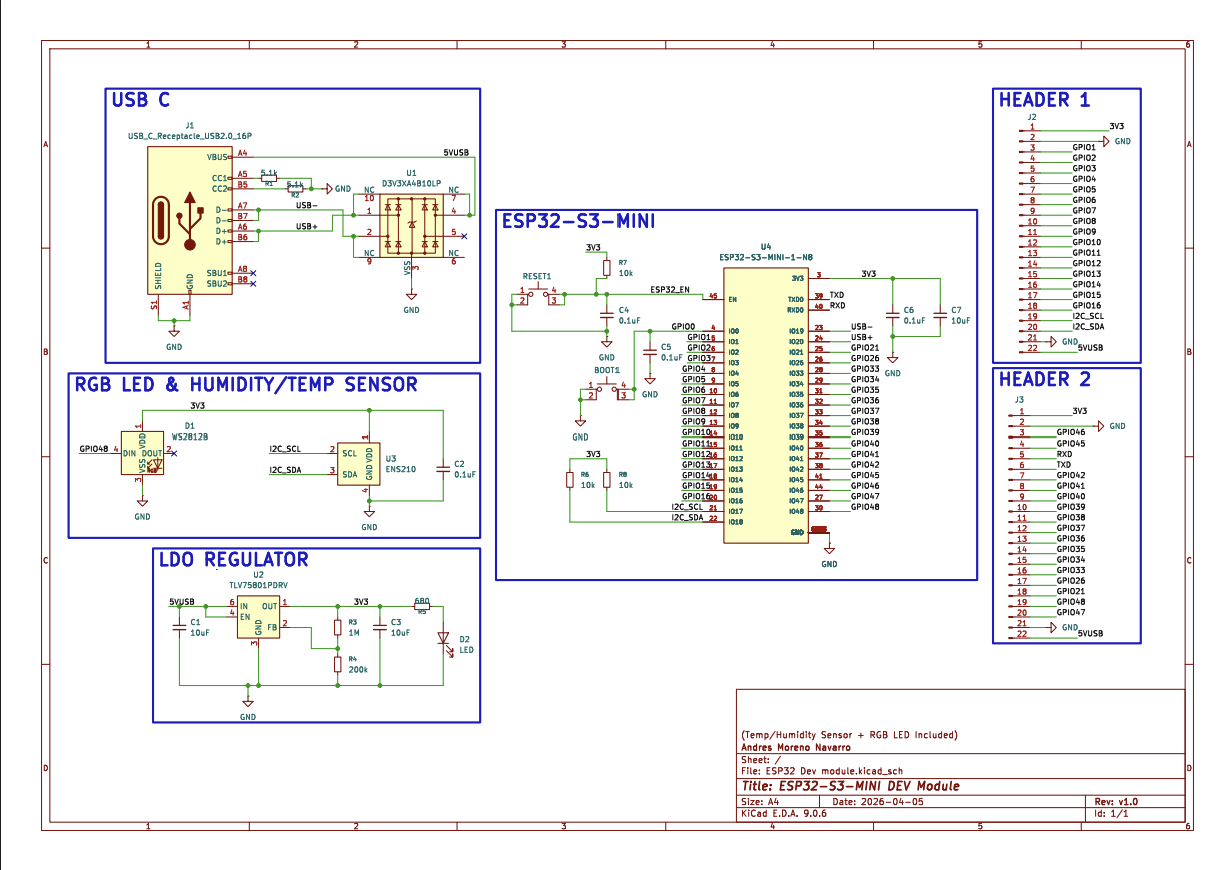

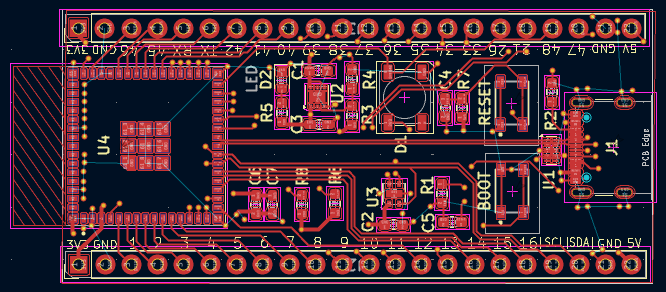

This is a custom development board built around the ESP32-S3-MINI-1-N8 — Espressif's compact Wi-Fi and Bluetooth 5.0 module. The goal was to design something equivalent to a commercial dev board entirely from scratch: full control over every component, every trace, and every design decision. It breaks out all usable GPIOs, adds an on-board temperature and humidity sensor, an addressable RGB LED, and powers from a single USB-C cable or 5V rail.

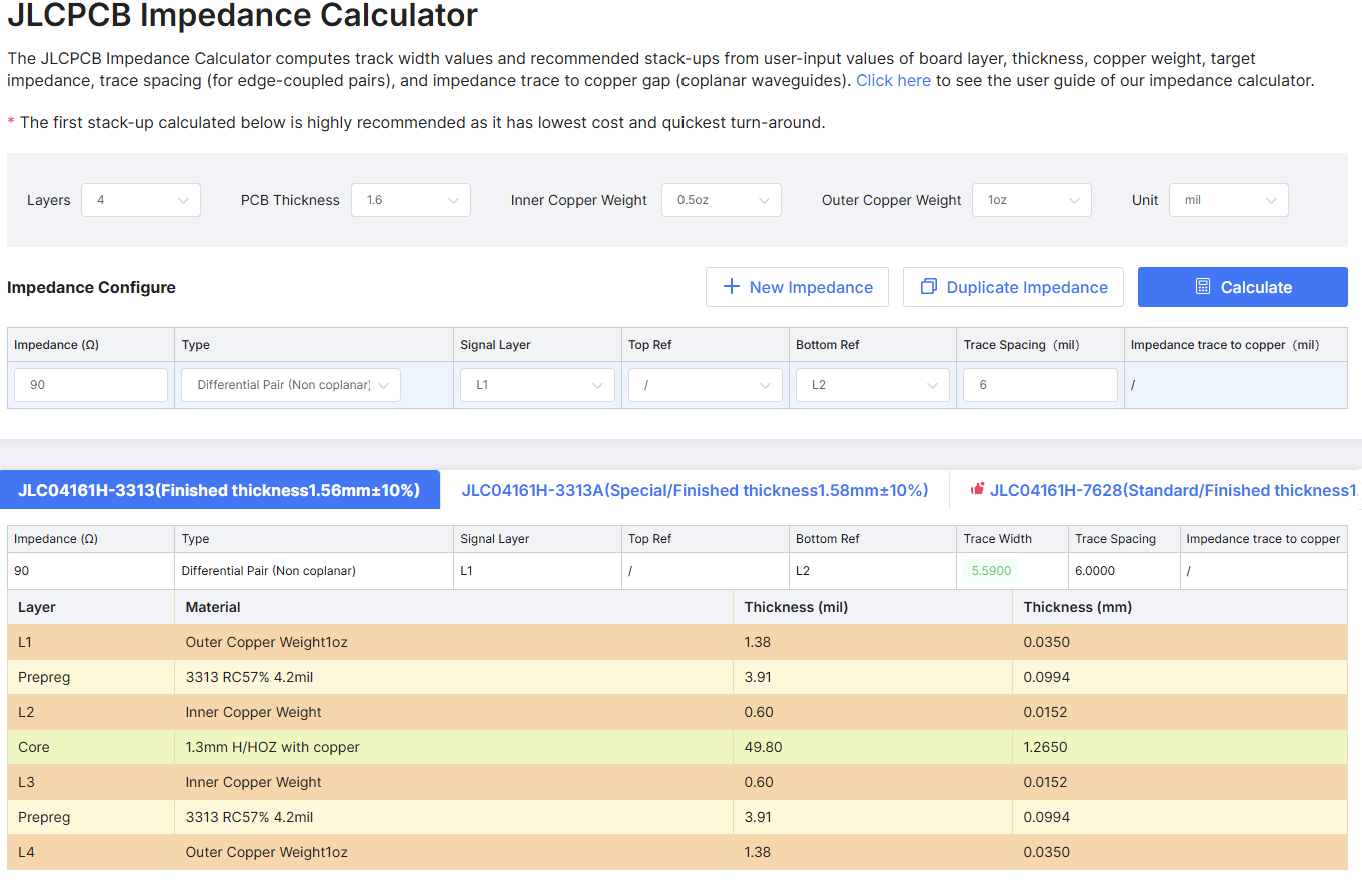

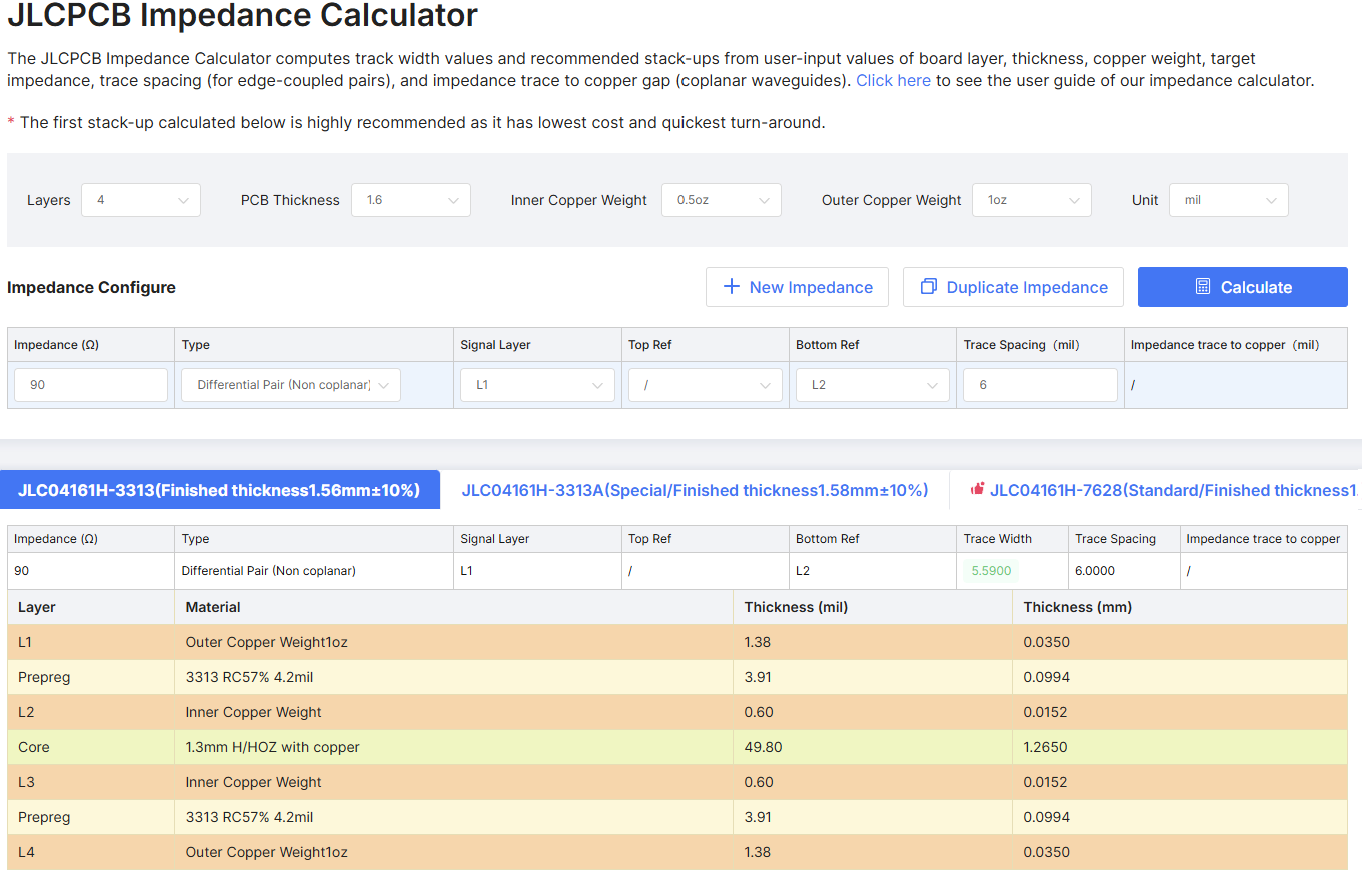

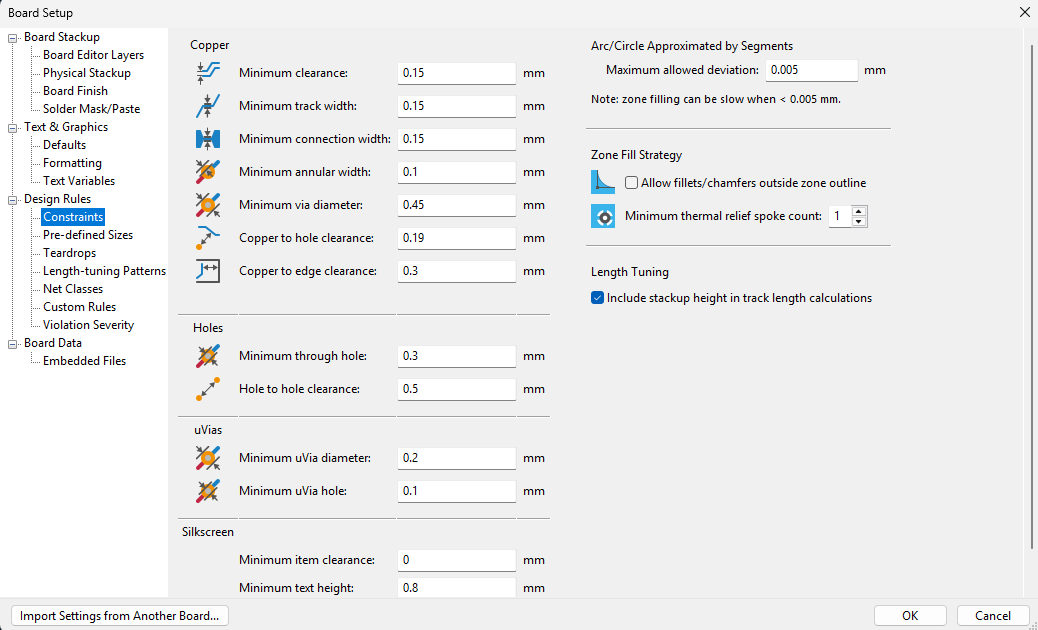

The entire design was done in KiCad 9, from schematic capture through to manufacturing-ready Gerber files, targeting JLCPCB's 4-layer process with the JLC04161H-3313 stackup. The USB differential pair was analysed for impedance using IPC-2141 calculations matched to that specific stackup, and all design rules were verified clean before ordering.

This was completed as an independent project during second year Electrical and Electronics Engineering at the University of Western Australia.

⚠ Note: The 3V3 header pin is a regulated output only — do not apply external voltage to it. The TLV75801 LDO has no back-drive protection; powering through 3V3 with USB disconnected will damage the IC. Power the board via USB-C only. See Rev 2 for a planned fix.

GPIO Pinout Reference

A complete pinout reference for both headers is available below. Every pin is listed with its GPIO number and all alternate functions — ADC, touch, RTC, UART, SPI, JTAG, and I²C — verified against the ESP32-S3-MINI-1 Datasheet v1.2. Strapping pins (GPIO45, GPIO46) are clearly flagged since they affect boot behaviour and should be treated with care in your own designs.

Full interactive pinout reference with color-coded function tags and connector lines to each pin pad.

📌 Open Full Pinout Reference →Bill of Materials

| Reference | Part Number | Description | Qty | Notes |

|---|---|---|---|---|

| Microcontroller | ||||

| U4 | ESP32-S3-MINI-1-N8 | Main MCU — Wi-Fi / BT5.0 / 8MB Flash | 1 | GPIO19/20 USB D±, not broken out to headers. |

| Power | ||||

| U2 | TLV75801PDRVR | 800mA LDO Regulator — 5V → 3.3V | 1 | WSON-6. RθJA = 80.3°C/W. Thermal pad to GND. |

| R3, R4 | 1MΩ / 200kΩ | LDO Output Voltage Setting | 2 | Feedback divider — sets TLV75801 output to 3.3V. |

| USB & Protection | ||||

| J1 | USB4105-GF-A | USB-C Receptacle — 16P Top Mount | 1 | CC1/CC2 pulled to GND via 5.1kΩ — signals USB device mode to host. |

| U1 | D3V3XA4B10LP | 4-line USB TVS ESD protection | 1 | UDFN-10. Protects VBUS, D+, D−. |

| R1, R2 | RC0603FR-075K1L | 5.1kΩ USB-C CC Resistors | 2 | Signals UFP (device) mode to USB host. |

| Sensors & Indicators | ||||

| U3 | ENS210-LQFM | Temperature & Humidity Sensor — I²C | 1 | QFN-4. SCL→GPIO17, SDA→GPIO18. |

| D1 | WS2812B | Addressable RGB LED — PLCC4 | 1 | GPIO48 data line. 3.3V powered — below WS2812B min. VDD (3.5V), see Rev 2. |

| D2 | 150060RS75000 | Red Status LED — 0603 | 1 | Power-on indicator. Current limited by R5. |

| R5 | RC0603FR-07680RL | 680Ω LED Current Limiter | 1 | Series resistor for D2 status LED — ~1.9mA at 3.3V. |

| Passives | ||||

| C2, C4, C5, C6 | CC0603KRX7R7BB104 | 100nF Decoupling Capacitor — 0603 | 4 | Placed adjacent to each IC power pin. |

| C1, C3, C7 | CL10A106MQ8NNNC | 10µF Bulk Capacitor — 0603 | 3 | LDO input, LDO output, and 3V3 rail. |

| R6, R7, R8 | RC0603FR-0710KL | 10kΩ Pull-up Resistors | 3 | EN (R7), I²C SCL (R6), I²C SDA (R8). |

| Connectors & Buttons | ||||

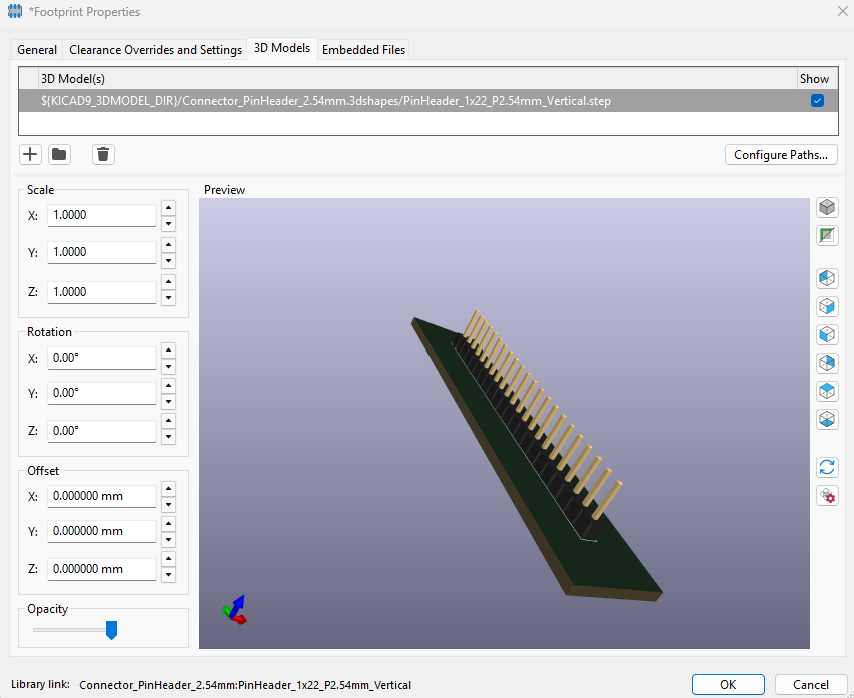

| J2, J3 | 61302211121 | 1×22 Pin Header — 2.54mm vertical | 2 | Full GPIO breakout, 2.54mm pitch. |

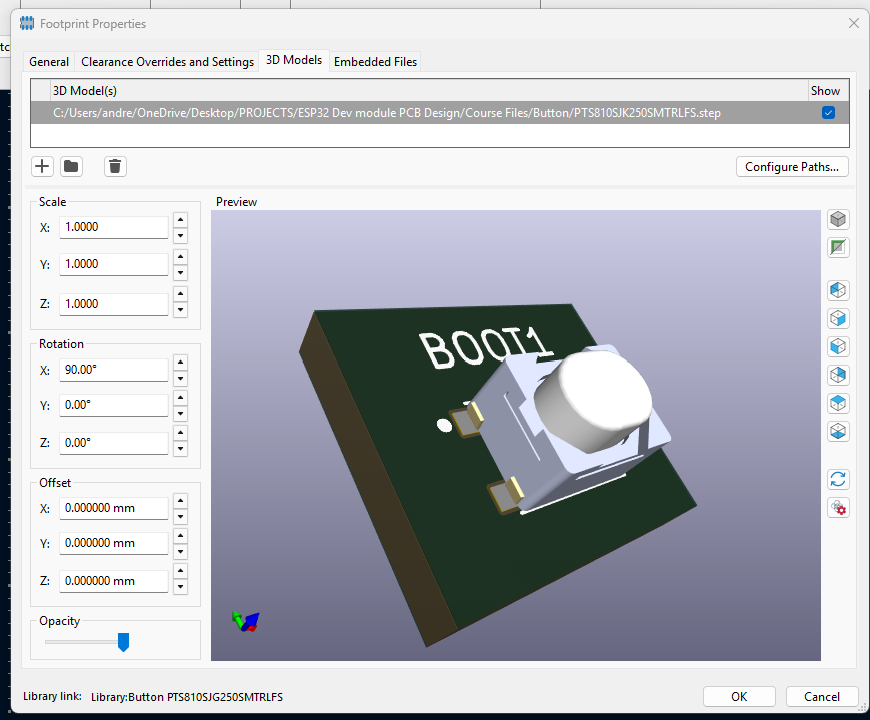

| BOOT1, RESET1 | PTS810 SJG 250 | SMD Tactile Button — SPST | 2 | BOOT→GPIO0, RESET→EN. |

Design Specifications

Design Process

Key Engineering Decisions

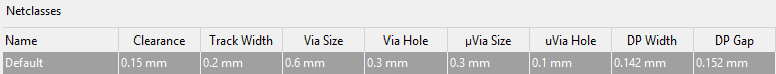

GPIO19 (D−) and GPIO20 (D+) instead of a CP2102N bridge. Eliminates one IC and reduces BOM cost without sacrificing programming or debug capability.h = 0.0994 mm, Dk = 4.4) gives a target width of 0.142 mm (5.59 mil) at 0.15 mm spacing for exactly 90 Ω. The pair was routed at 0.15 mm using the default netclass — slightly wider than the 0.142 mm target, giving an estimated impedance of ~88 Ω — well within the USB 2.0 Full Speed tolerance of 90 Ω ±15%.GPIO0 is reserved for the BOOT button, EN for the RESET button, and GPIO19 (D−) / GPIO20 (D+) are routed directly to the USB-C connector — none of these are safe or useful to expose on a general-purpose header. The four positions freed up are replaced with additional power and ground pins: each header provides 3V3 and GND at the top (pins 1–2) and a second GND and 5V VBUS at the bottom (pins 21–22). This gives two ground references per header, which is practical for breadboard use and reduces the chance of floating grounds when connecting peripherals.RθJA = 80.3°C/W vs 176.9°C/W. At 300mA load (P = 0.51W), WSON-6 gives only +41°C junction rise vs +90°C for SOT-23. Thermal pad soldered to GND copper pour.Design Verification

(1 warning excluded)

Future Improvements — Rev 2

100kΩ / 20kΩ, maintaining the same output voltage while lowering source impedance and improving noise rejection.3V3 header pin is a regulated output only — do not apply external voltage to it. The TLV75801 LDO has no reverse current protection; powering through the 3V3 pin with USB disconnected back-drives the LDO output and can damage the IC. Rev 2 will add a series Schottky diode or ideal diode load switch on the LDO output, which will block reverse current and make it safe to power the board from an external 3.3V supply — enabling the board to run without USB-C.